晚上回來後,想說來替 Vim 加一個功能好了XD

之前在 trace Verilog 訊號時,會一併顯示目前所在的 module name 以及行數,可以很快知道 trace 訊號有沒有過頭了。

但是很多時候,我們好奇的是這根訊號它又被穿到哪個 module or cell 了!

如果是 cell 那還好辦,畢竟 pin 不會太多。

假設是另一個 module 或是 hard macro,此時 pin 的個數便會很多,甚至在一頁內都看不到 instantiation 的地方?

雖然可以用搜尋的方式找到分號,接著找右大括號,然後用 % 跳到左大括號,如此一來,我們就可以看到 instantiation 的 module name or cell name 了!

不過,如果可以比照 module 一樣處理,工作當然更方便。

可惜,這次用 Google 搜尋 Vim script 關鍵字都不順利,Vim help 又不好閱讀,於是直接詢問 Gemimi,想不到比我用 Google 快?

結論就是我又可以豐富我的 vimrc 了XD

2025/06/23 更新

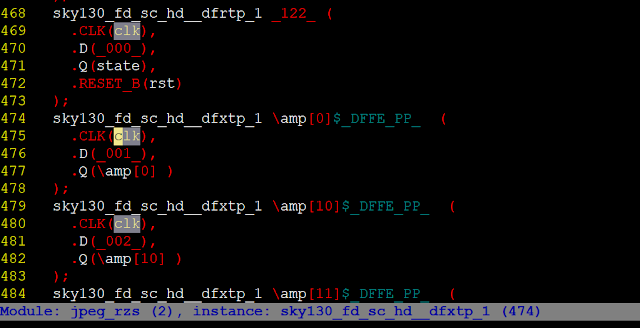

今天去辦公室馬上拿真實的 netlist 來測試,果然還不錯,除了要稍微修改 regex 外,畢竟,真實的 netlist pin 很多,我原本的假設不一定成立!

不過,重點還是 [".", "(", ")"] 這 3 個字元是否存在於 hightlight 那行,假設有任一個存在,我就當作是 instantiation 語法!

目前使用的感想還行XD

沒有留言:

張貼留言