在 Linux 可以安裝 universal-ctags,Windows 上也有對應版本可裝,不過 Windows 需要額外準備 gtags.conf。

執行 gtags 時只要加上 --gtagslabel new-ctags 即可,這樣針對 Verilog 檔案便會呼叫 ctags 來 parsing。

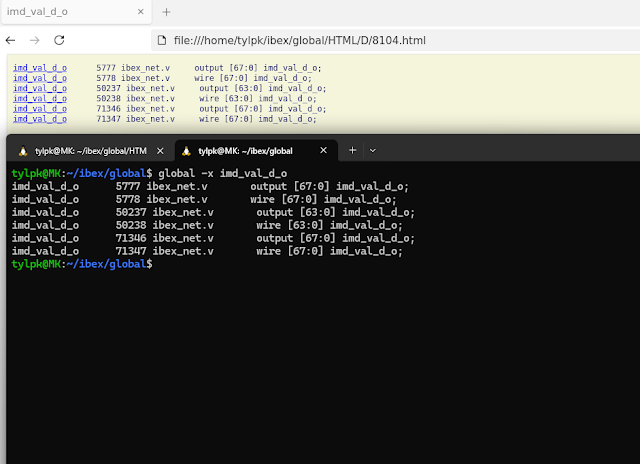

目前看起來不管是 gtags、htags -sna、global 都可以正常執行。

當輸入是 netlist 時,由於 design 集中在一個檔案中,這會導致 htags 產生的單一檔案 html 過大,我公司電腦自己已經加到 16G 記憶體,但還是因為使用記憶體過多導致 chrome 會讀不完整個檔案一直在轉圈圈,不過使用 global 查詢都正常。

改用 ORFS 的 ibex 來當例子測試看看。

目前有一個想法,想要在 global 的基礎上動些手腳,將選示行號的地方改成 module name,這樣對 trace signal 比較有幫助。

所以流程大概是這樣。

01. 呼叫我的程式,傳入 netlist。

02. 執行 gtags 得到 3 個資料庫檔案。

03. 將 netlist 的每一行建立 map 對應,據實測即使 netlist 有 3000 萬行,大概也是 10 ~ 20 秒就可以建立完畢,也就是用空間換取時間的做法。

04. 程式進入 while loop,監聽剪貼簿或是 socket。

05. 收到 Vim 傳來的 signal 便呼叫 global 查詢。

06. 將圖片的查詢結果中的行號改成 module 並顯示改過的結果。

另外,今天有查詢了一下資料,目前看來 DVT Eclipse IDE 也許是一個可以試試的工具,不過需要掏出魔法小卡而且似乎是訂閱制?

沒有留言:

張貼留言