2021 年買了暗黑 2 重製版 PC 版遊戲後,由於手上滿 7 歲的筆電沒有獨顯,故無法執行遊戲!後來又把打算換機的預算挪去

做好事,一直等到

2022 年端午節前夕才狠下心來購買 Switch 主機以及暗黑 2 重製版 Switch 版遊戲,也算回味一下當年畢業後玩過的少數幾款遊戲之一,記得當年玩過死靈法師後就因工作繁忙沒有下文了,也不太有印象當初手上為何有那款遊戲?

從 2022 年端午節開始,陸續玩了死靈法師、雙熱丁、旋風蠻、槌丁、電法、弓馬、

標馬、召德、冰法、馬賽克刺客、又一隻雙熱丁以及最後的天拳丁,很多角色都是在半夜睡不著覺的夜晚練起來的,就如同今天

凌晨 4 點起來關心洛杉磯的街頭一樣XD

雖然也不是每天都在玩,但陸續也投資了不少時間在上頭,這條路總有走到盡頭的時候。

可惜人生總有遺憾,尤其是暴雪不合理的升級經驗懲罰制度,實在是逼人花時間去玩遊戲!

雖然不玩了,還是記錄一下未完成的代辦事項。

01. 槌丁扮盾丁 atking

這隻由

雙熱丁起家,9X 級後邊打紅門邊轉槌丁以及邊農裝備養家,配合

單機複製大法複製打到過的特大板,最高傷害可以來到 15K 左右,幾個月前又悟出戰召權杖配裝後,雖然傷害只剩 12K,但什麼場景皆可通刷,只差打紅門時要不斷的喝紫水,整體來說也算是盡顯王者風範。

上圖是升 97 前抓的圖,盔甲也還只是法鎧,中間有過渡穿灰暮罩衣,最後則是穿龍皮甲的謎團,這樣好處是防禦可以多快 200,壞處是要額外點力量。

目前只差升到 98 就可以補齊專注靈氣的最後 1 點技能點,如果要開聖護打紅門則需要升到 99 級,當然也可以不點救贖改用權杖自帶的救贖技能,缺點是切執法者就不能使用救贖。

02. 跟小老婆同名的冰法 Clare

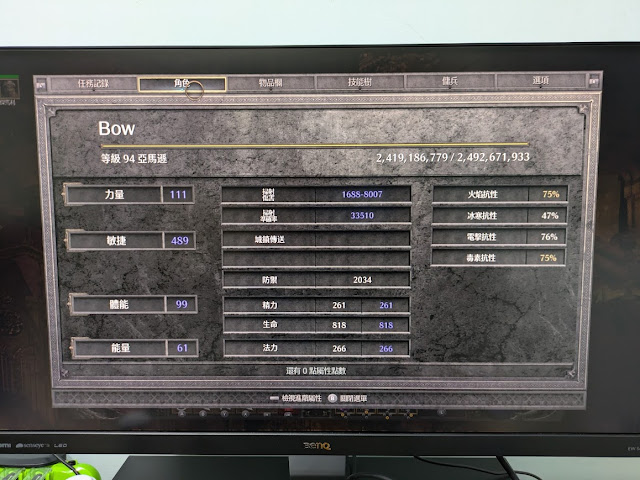

03. 手感最好的弓馬 Bow

技能點在 94 已差不多點齊,就差戰旅鞋未曾打到,目前掃射應該是 8K 左右。

賭百抗鞋的相關注意事項

clvl = character level 角色等級

mlvl = monster level 怪物等級

ilvl = item level 物品等級

a. 等於怪物身上掉的 ilvl = mlvl

b. npc 出售物品 ilvl = clvl + 5,但普通難度有上限

c. 賭博時 ilvl = clvl - 5 ~ clvl + 4

d. 洽西注入 ilvl = clvl + 4

e. 隨著方塊公式改變

f. 翻箱掉落 ilvl = area level

qlvl = quality level 品質等級

不同物品有不同等級

magic_lvl = magic level 魔法等級

只有少數物品有,比如權冠

alvl = affix level 魔法字首尾等級

百抗鞋就是要看這個,來決定要用什麼等級角色賭什麼物品。

先決定你要的詞彙 alvl,再看你要賭的鞋 qlvl,便知道 ilvl 用多少等級角色,小數點是無條件捨去。

可以直接看此

Youtuber 的影片或是 ptt Diablo 精華區 z-2-3-9-3。

如果賭皮靴,魔法字首尾只要 30% 高跑,10% 打擊恢復以及百抗:

alvl = 37

qlvl = 3

利用 11 行公式可以得知,ilvl = 38,因為賭博物品最少為 clvl -5,故得知 clvl = 43,也就是用 43 級人物去賭皮靴即可,由於我們有壓制 alvl,可以避免出現我們不要的詞彙。

但據我賭了八千萬左右的經驗得知,一切還是看臉,我最多得到相加 80 出頭的抗性而已。

我玩了2 年,也只打到過兩雙百抗鞋,且不是單抗都超過 30,高跑也只有 10% 或 20 % 而已。

無意間試出的 Switch 單機複製大法

先開啟任一角色至少打滿 5 ~ 10 分鐘,儲存後改用另外一角色登入,接著迅速複製東西或錢並按下儲存離開,然後迅速按 Home 回到 Switch 桌面並按 X 完全關閉暗黑 2 遊戲。

之後用複製東西的角色檢查,被複製物品以及複製物品都在就是成功了!

95 升 96 單機八人難度經驗值

超市全打約 100 多萬(邪惡區域則有 31X 多萬)。

97 升 98 單機八人難度經驗值

超市全打約 23 萬(邪惡區域則有 100 多萬),只打巴爾五將軍及巴爾約 28 萬。

2024/11/09 更新

以下都是有遺產的情況下,除了火棒、火山頭、火法專用高施藍項鍊外,其餘該有的我都有了,包含精神劍盾、橡樹、戰召、大小毀符、技能板 N 片等,大部分的數值都是近頂。

40 幾等可以過普通,不用半小時就可以練到 50 等。

60 幾等可以過惡夢,不用半小時就可以練到 75 等。76 等打巴爾從第四層一路清過去,一次約可升 4 格,77 等時可升 3 格,78 等時可升 2 格。

78 等進地獄,約 83 等可到巴爾,85 等時過關,88 等時打巴爾從第四層一路清過去,一次約可升 2 格。

以上惡夢及地獄懶得慢慢過的關卡都是用飛的,比如第三關,第五關等。

另外在單機複製東西時,假設人物已達上限 28 個記錄檔,最後創建的人物會被清掉以及最後一個開啟的記錄檔其人物技能快速鍵會被清空需要重設。

2024/11/20 更新

最後確定即使只建立 27 個角色,當使用複製大法時,第 27 個人物記錄檔技能快速鍵會被清空需要重設。

另外 90 等時,世界之石邪惡區域,從第二層一路打過去,視怪物數量不定,經驗值可以上升 0.5 ~ 1.5 格,91 等時大概只剩半格多。

結論就是,想練新角色時,大概升到 92 等就好,再來就太累了。

常用角色畢業需要等級

電法 94 等

冰法 96 等

火法 98 等(包含火蛇)