坦白說,我一直很不喜歡 Synopsys!

尤其最近的一個工作項目是要跑他提供的 IP Testbench。

大部分情況下,我們從客戶那拿到的 input 都是 netlist,所以,IP 相關的文件會提到如何做客戶 design 的 gatesim!(實際上,他文件寫的對我解決問題都沒幫助!)

雖然我們客戶某些 rtl 資料夾不想給我們,但因為那本來就跟 netlist 無關,故不給好像也還合理?

但是當使用 NCVerilog 編譯的時候,連 Synopsys 自己 Testbench 的相關檔案編譯都會有錯誤,這我實在是不能接受!

我能接受你只給 vcs 的 Testbench,但既然你有 option 可以選擇,理論上你應該要測試過沒問題才對?

但從昨天中午拿到客戶最後給的 C code 檔案後,我都一直在解決編譯的錯誤,直到今天晚上 10 點左右,我才順利跑起 simulation!

雖然這兩天大部分的時間都在跟我同事看他 Testbench 的問題,即使扣掉開會及上課的時間,我應該至少也花了 4 ~ 5 個小時有,真的是浪費我的生命XD

拿這些時間多寫幾個 Vim functions 來幫助我工作不是更好嗎?

不如歸去呀XD

2025/06/27 更新

果然如我預期,早上上班登入工作站看到的結果是失敗。

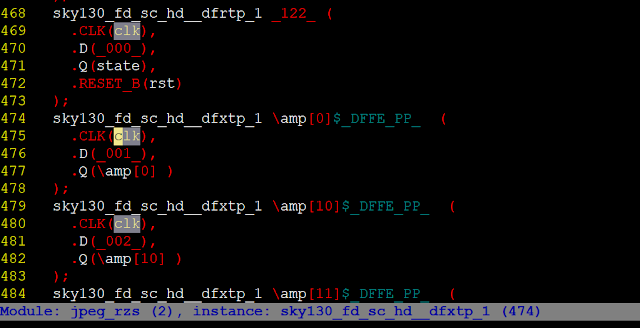

此時第一件事一定是 dump waveform,優先檢查的是 clock 和 reset。

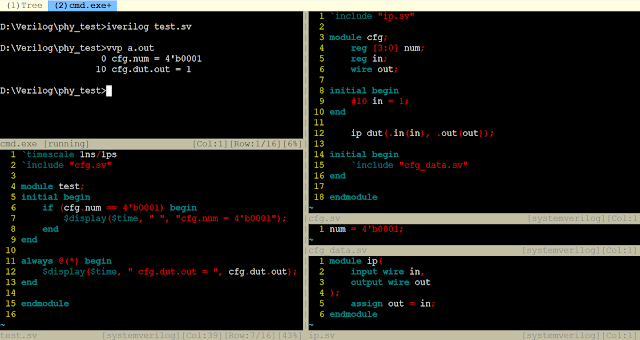

不過,Synopsys 提供的 define 打開就會報錯!還好這個錯誤是可以 Google 到的,只是 LD_PATH 設定的問題,不過,我自己得先補一個 NCVerilog 參數。

但在我一時還找不到 LD_PATH 該設的正確路徑時,為了不浪費中午的時間,於是自己寫一個 initial block 直接 dump VCD 最快,只要硬碟不要爆掉就好XD

稍微看了一下似乎沒看到異常的訊號?

下午只好又繼續翻閱各個文件。

晚上回家連回公司時,忽然想到何不試試 JTAG protocol?

雖然最簡單的 REVISION_CHECK 可以通過,但其他都會報錯,暫時還想不到解法,不過我應該會往自己有修改過的 Verilog 檔案去下手檢查?

2025/06/28 更新

雖然本來就有打算放假連回公司繼續測試,但每測試一次就要等一陣子,實在緩不濟急。

還好,據我多年 coding 經驗,EDA 只要還是由軟體人所開發,我大概就能知道他們是如何設計的?

雖然我可以無腦的複製一份最上層的資料夾再做另一個測試,但是很多 file_list 路徑都要修改,當然這也不是什麼太困難的事,但最麻煩的是我的工作站空間已經不足,我連 dump VCD 都不夠了,雖然我可以 dump fsdb,但不知為何似乎是 license 原因,我無法開啟 fsdb 檔案,故我還是需要 VCD 比較實在。

為了不浪費空間,而我的多個測試也不需要更動 Testbench 內容,最多只是調整 test script 參數。

最好的方式就是只複製 test script、test script 裡面用到的檔案(比如說直接透過 command line 傳給 xrun 的,非 file_list)、幾個 include 檔案(位在測試路徑下的,這些才是動態產生的,原本就在 Testbench 那包的,大部分都不需要修改,故用同一份即可),這些就是我最低限度的檔案,只複製這幾個檔案,我隨時可以長出好幾個測試,這樣更能加速我驗證收斂問題。

現在能限制我的就只剩下 NCVerilog license 個數了!

但我家只有 2 個呀XD