Ans:使用 generate 語法即可,generate for block 要不要命名都可以,這應該是目前最方便的 workaround 了。

`timescale 1ns/1ns

`define VIEW 1

module test;

initial begin

if (`VIEW == 1) begin

$dumpfile("wave.vcd");

$dumpvars(0, test);

end

end

reg [3:0] buffer[0:7];

genvar j;

generate

for (j = 0; j < 8; j = j + 1) begin: buffer_array

wire [3:0] buff;

assign buff = buffer[j];

end

endgenerate

integer i;

initial begin

for (i = 0; i < 8; i = i + 1) begin

#10;

buffer[i] = i[3:0];

end

#200;

$finish;

end

endmodule

2023/12/27 更新

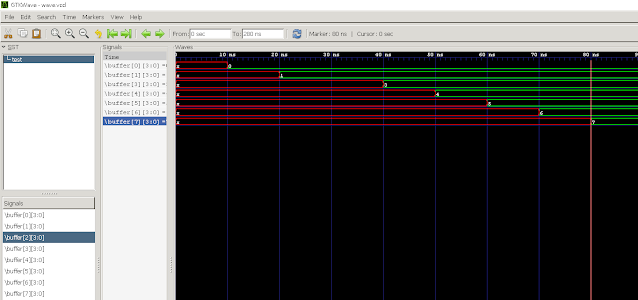

還有另一個作法是使用 $dumpvars,這個似乎是 iverilog 作者在回網友郵件中建議的?這個語法更少,雖然 vpp 模擬時會有 warning,不過在 GTKwave 中不會多一個臨時變數,看起來更直觀,但似乎不是都可以用?請詳此處。

沒有留言:

張貼留言